# Electrical Characterisation of Poly(vinyl alcohol) based Organic Field Effect Transistors

Dissertation zur Erlangung des akademischen Grades

Doktor der technischen Wissenschaften

Angefertigt am Institut für Physikalische Chemie

Eingereicht von:

Dipl.-Ing. Martin Egginger

#### Betreuung:

o. Univ. Prof. Dr. Mag. Niyazi Serdar Sariciftci

#### Beurteilung:

Erstbeurteiler: o. Univ. Prof. Dr. Mag. Niyazi Serdar Sariciftci

Zweitbeurteiler: o. Univ. Prof. Dr. Siegfried Bauer

Linz, Mai 2009

für July in inniger Liebe

# **ACKNOWLEDGEMENT**

First and foremost I want to thank Professor Niyazi Serdar Sariciftci who enabled and supervised this dissertation.

I am also very grateful to Professor Siegfried Bauer for his supervision, his ideas and his humour. Thanks to all members of the SoMaP group, especially Reinhard Schwödiauer and Mihai Irimia-Vladu for the good collaboration and Francisco Camacho-Gonzales and Johann Leonhartsberger who helped me foaming some polymers.

I want to thank my "Physics-Primer" Robert Köppe for endless discussions, Philipp Stadler for always critically questioning my theories and Helmut Neugebauer, whos comments are always dead-on.

Special thanks go to Gilles Dennler, Anita Fuchsbauer, Christoph Lungenschmied, Nenad Marjanovic, Beatriz Meana Esteban and Barbara Stadlober for all the fruitful discussions and to Serpil Tekoglu and Johanna Novacek who contributed some OFET measurements during their visits at LIOS.

I want to show my apprecitation to the most important people of the institute: Petra Neumaier and Birgit Paulik who smoothen all administrative waves in the secretariat, Manfred Lipp for excellent technical assistance and Gerda Kalab who is taking care of the LIOS labs.

Andreas Tanda from plastic electronic is thanked for the good collaboration and Alberto Montaigne Ramil for providing AFM images.

X-ray measurements were done in Graz by Heinz-Georg Flesch from Roland Resel's group: many thanks!

Markus Himmelsbach and Wolfgang Buchberger are acknowledged for helping me with the AAS measurements.

Robert Fuss (Kuraray Specialities Europe KSE GmbH, Germany) is thanked for providing PVA.

Enn Mellikov, Dieter Meissner und Tiit Varema enabled my visit at the Tallinn University of Technology.

I want to express my gratitude to the people that nowadays share their office with me and that work together with me in the quickly growing CO2 project: Ercan Avci, Martin Kruijen, Edina Mujcinovic, Kerstin Oppelt, Engelbert Portenkirchner and Peter Trefflinger. I want to thank all the other members of LIOS (some of them left already) for the good collaboration: Elif Arici-Bogner, Erika Bradt, Daniel Egbe, Pinar Frank, Jacek Gasiorowski, Serap Gunes, Wolfgang Huber, Sandro Lattante, Shengli Lu, Gebi Matt, Farideh Meghdadi, Le Huong Nguyen, Almantas Pivrikas, Hans Jürgen Prall, Adem Sahin, Stefan Schaur, Birendra Singh, Andreas Spiegel, Patchanita Thamyongkit and especially everybody who is not on this list, but should be there!

Last but not least I want to thank my family for all their support, especially July for her love and her patience when I was in the labs till late at nights.

domo arigato gozaimasu

## ZUSAMMENFASSUNG

Eine Vielzahl an wissenschaftlichen Erkenntnissen und technologischen Fortschritten bei der Herstellung und Charakterisierung organischer Feldeffekt-Transistoren (OFETs) während den letzten zwei Jahrzehnten hat es ermöglicht, dass erste Produkte mit organischer Elektronik am Markt sind. Gedruckte organische Elektronik umfasst Widerstände, Dioden und Transistoren und kann eine billige Alternative zu Silizium-basierten Systemen sein, im Speziellen bei großflächigen und flexiblen Anwendungen.

Neben der Langzeitstabilität ist eine gute Reproduzierbarkeit der Strom-Spannungs (I-V) Kennlinien ein essentieller Parameter für die Verwendung dieser Bauteile. Diese I-V Kennlinien können eine Hysterese zeigen, was bei OFETs sehr häufig beim Messen einer Transfer Charakteristik [einer Variation der Gatespannung (V<sub>GS</sub>)] beobachtet wird. Es gibt vielfältige physikalische Gründe, die eine derartige Hysterese verursachen können, aber vergleichende wissenschaftliche Untersuchungen zu den unterschiedlichen Hysterese Phänomenen sind rar und ein umfassendes Bild der "Hysterese in OFETs" fehlt in der Literatur.

Das erste Kapitel dieser Dissertation gibt einen ausführlichen Überblick zu verschiedensten physikalischen Effekten, die Hysterese verursachen können und exemplarische Beispiele aus der Literatur werden diskutiert.

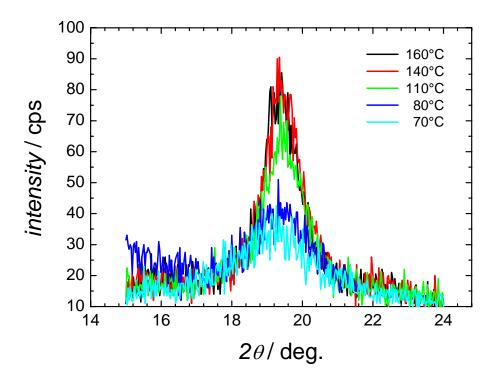

Detaillierte experimentelle Untersuchungen an OFETs, die Poly(vinyl alkohol) (PVA) als Dielektrikum verwenden, zeigen, wie die - aus der Literatur bekannte - Hysterese in diesen Bauteilen durch einen einstufigen Reinigungsschritt des PVAs minimiert werden kann. Temperaturabhängige Messungen, dielektrische Spektroskopie und Röntgen-Messungen vervollständigen das Bild der Hysterese in PVA basierten OFETs.

Die unterschiedlichen Bauweisen hysterese-freier OFETs werden im letzten Kapitel untersucht und verglichen: top gate versus bottom gate und coplanar versus staggered. Im Rahmen dieser Untersuchungen wurden erstmals top gate OFETs, die PVA, das aus wässriger Lösung auf den organischen Halbleiter aufgetragen wird, verwenden, hergestellt und charakterisiert.

# **ABSTRACT**

Research on Organic Field Effect Transistors (OFETs) has made significant advances both scientifically and technologically during the last decade with first products soon entering the market. Printed electronic circuits using organic resistors, diodes and transistors may become cheap alternatives to silicon based systems, especially in large area and flexible applications. A key parameter for device operation is, besides long term stability, the reproducibility in the current-voltage behaviour, which may be affected by hysteresis phenomena. Hysteresis effects are often observed in organic transistors during sweeps of the gate voltage ( $V_{GS}$ ). The origin of such hysteresis can be manifold, but comparative scientific investigations are rare and a comprehensive picture of "hysteresis phenomena" in OFETs is still missing.

The first section of this thesis gives a detailed overview on physical effects that can cause hysteresis and comparatively discusses the importance of such effects in OFETs.

Detailed experimental investigations on hysteresis in poly(vinyl alcohol) (PVA) based OFETs show how hysteresis in these devices can be minimized by a one step cleaning procedure. Temperature dependent measurements, dielectric spectroscopy and x-ray measurements complete the picture of hysteresis in PVA based OFETs.

Finally hysteresis free OFETs are used to investigate various OFET structures: top gate or bottom gate and coplanar or staggered, respectively. This is the first report on top gate OFETs using PVA (deposited from aqueous solution) as dielectric.

# **TABLE OF CONTENTS**

| 1 | INTRODUCTION                 |      | UCTION                               | 1  |

|---|------------------------------|------|--------------------------------------|----|

|   | 1.1.                         | OFF  | ET Basics                            | 3  |

|   | 1.2.                         | Hys  | teresis                              | 10 |

|   | 1.2.1.                       |      | Examples from Inorganic Transistors  | 10 |

|   | 1.2.2.                       |      | Hysteresis in OFETs                  | 11 |

|   | 1.2.                         | 3.   | Hysteresis mechanisms                | 15 |

|   | 1.3.                         | Diel | ectric Spectroscopy                  | 29 |

| 2 | EXI                          | PERI | MENTAL                               | 35 |

|   | 2.1.                         | Mat  | erials                               | 35 |

|   | 2.1.                         | 1.   | Poly(vinyl alcohol)                  | 35 |

|   | 2.1.                         | 2.   | Organic Semiconductors               | 38 |

|   | 2.2.                         | Dev  | ice Preparation                      | 38 |

|   | 2.3. Cur                     |      | rent voltage measurements            | 39 |

|   | 2.4.                         | Diel | ectric spectroscopy                  | 40 |

|   | 2.5.                         | AFN  | M measurements                       | 40 |

|   | 2.6.                         | X-ra | ny measurements                      | 41 |

| 3 | RESULTS and DISCUSSION       |      | S and DISCUSSION                     | 42 |

|   | 3.1.                         | Hys  | teresis in PVA based OFETs           | 42 |

|   | 3.1.                         | 1.   | Ions in PVA                          | 42 |

|   | 3.1.2.                       |      | Temperature dependent hysteresis     | 50 |

|   | 3.1.                         | 3.   | PVA crystallinity                    | 53 |

|   | 3.2.                         | Dev  | ice geometry                         | 58 |

|   | 3.2.                         | 1.   | Staggered versus Coplanar Geometries | 58 |

|   | 3.2.2.                       |      | Top Gate OFETs                       | 63 |

| 4 | SUI                          | ΜМА  | RY and CONCLUSION                    | 67 |

| 5 | REI                          | FERE | NCES / BIBLIOGRAPHY                  | 70 |

| C | URRIC                        | ULU  | M VITAE                              | I  |

| E | Eidesstattliche Erklärung IV |      |                                      |    |

# 1 INTRODUCTION

The first thin-film transistor (TFT) was reported in 1962 by *Paul K. Weimer* [1]. Twenty years later the first reports on organic field effect transistors (OFETs) using organic semiconductors on inorganic dielectrics appeared [2, 3, 4]. Pioneering work towards allorganic OFETs testing various organic dielectrics was done by *Peng* and coworkers [5]. Various examples for the applications of OFETs, *e.g.* large area electronic applications, printed electronics, electronic paper (e-paper) [6], electronic skin, etc. are documented in Ref. [7]. For many applications, speed is no more a limiting issue, since up to 2 MHz operation has been demonstrated in OFET circuits [8]. Companies presented printed logic circuits for RFID tags [9], for a cell phone with an electrophoretic display, addressed by an active matrix OFET backplane [10], and a backplane OFET array for e-paper [11].

The enormous interest in the field of OFETs [7, 12] is documented by various scientific review articles on charge transport [13, 14], on semiconductors for OFETs [15], on gate dielectrics [16,17], on progress in plastic electronic devices [18] and on OFETs as sensors [19, 20].

Although first products using OFET technology are already entering the market, a number of issues still needs basic scientific investigations: Device stability is a very important topic, closely related to hysteresis and threshold voltage shifts due to bias stress. Also some details of the fundamental working principle of OFETs like gate voltage dependent contact

resistance, access resistance, mobility and others are still under discussion. These parameters are closely related to device architecture and material processing.

In the following subsections of the introduction an overview on the basic parameters describing an OFET is given, followed by a review on hysteresis in OFET literature. This chapter is based on an invited review that has been published in Monatshefte der Chemie – Chemical Monthly [21]. A short introduction to dielectric spectroscopy, a powerful tool to investigate the electrical properties of dielectric materials, completes the introduction. After the experimental section, detailed investigations on ions in poly(vinyl alcohol) and their influence on OFET characteristics are presented. The results from that section show how hysteresis free OFETs can be produced. Such OFETs are used in the last section to investigate different OFET geometries and their influence on device parameters, before finishing with a short summary and conclusions.

#### 1.1. OFET Basics

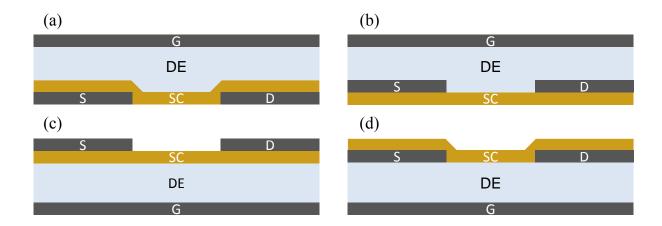

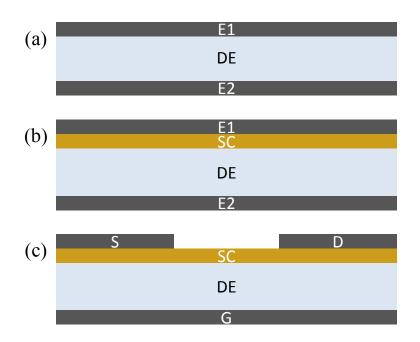

An OFET is a three terminal device, where one electrode (the gate) is separated from the other two electrodes (the source and the drain) by an insulating layer (the dielectric). The source and the drain electrodes are connected via an organic (n- or p-type) semiconductor with a defined geometry, the width W and the length L. The layers of the OFET are usually too thin to form a stable freestanding device, therefore OFETs are built on a substrate (e.g. glass, Si wafer or plastic foil). Depending on the layer deposition sequence, four different OFET structures can be realized, as shown in Figure 1.

**Figure 1:** Different structures of OFETs: (a) top gate staggered (top gate bottom contacts), (b) top gate coplanar (top gate top contacts), (c) bottom gate staggered (bottom gate top contacts) and (d) bottom gate coplanar (bottom gate bottom contacts). Source (S), drain (D), gate (G), semiconductor (SC) and dielectric (DE).

Two different nomenclatures are commonly used do describe the different OFET structures. One nomenclature focuses on the layer sequence, *e.g.* bottom gate bottom contact, which underscores the device production. The other nomenclature stresses the "active part" of the OFET: "staggered" or "coplanar". Important effects, *e.g.* "access resistance" or "current crowding", that will be described and discussed later, are emphasized by these names.

Current flows from the source electrode (S) to the drain electrode (D), upon applying a voltage between S and D ( $V_{DS}$ ). This current can be influenced by a voltage applied to a third electrode (gate). Applying a voltage to the gate ( $V_{GS}$ ) induces charges at the interface between

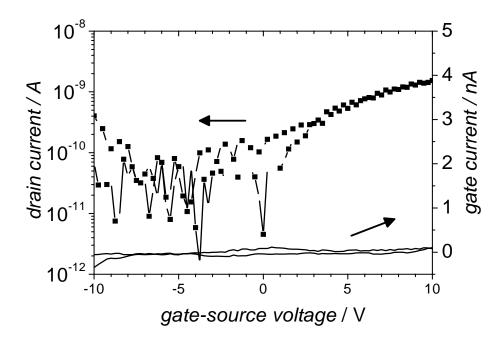

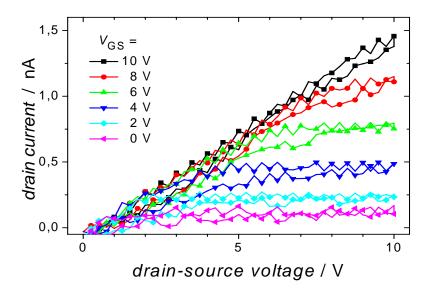

the dielectric and the semiconductor. The layer of accumulated charges at the semiconductor / dielectric interface is called channel. This channel enables current flow between source and drain ( $I_{DS}$ ). The conductive channel is formed in a few nm thin layer [22, 23, 24] at the semiconductor / dielectric interface. FETs are characterized by measuring transfer ( $I_{DS}$  versus  $V_{GS}$  at constant  $V_{DS}$ ) and output ( $I_{DS}$  versus  $V_{DS}$  at constant  $V_{GS}$ ) characteristics.

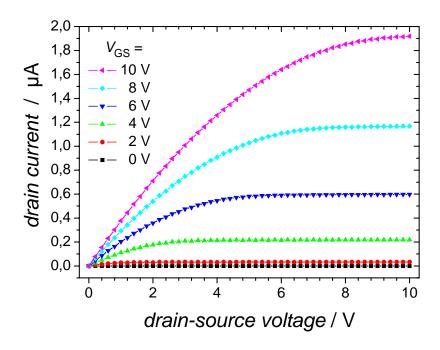

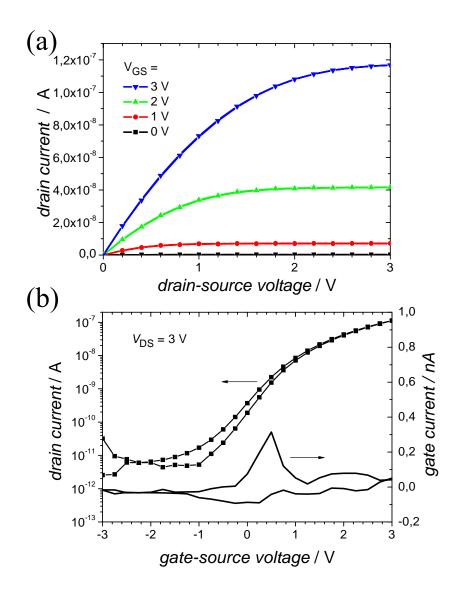

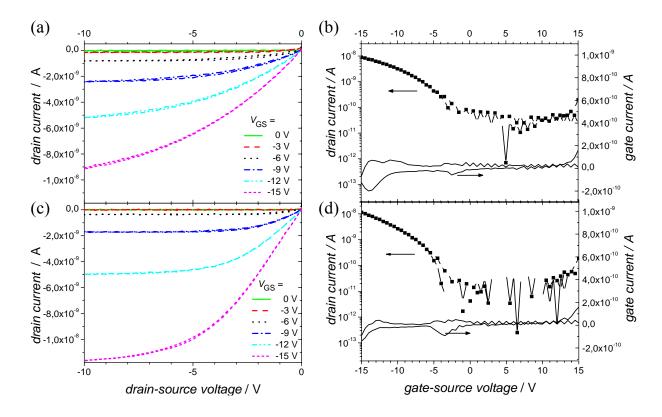

**Figure 2:** Output characteristics of a dialysis grade PVA / C<sub>60</sub> OFET.

In an output characteristics (shown in Figure 2)  $V_{\rm DS}$  is sweeped while a constant  $V_{\rm GS}$  is applied. If a positive  $V_{\rm GS}$  is applied to an n-type OFET,  $I_{\rm DS}$  will increase linearly with  $V_{\rm DS}$  increasing from 0 V to positive voltages. When  $V_{\rm DS}$  is as large as  $V_{\rm GS}$ , the field at the drain electrode is reduced to 0 and the channel "pinches off" and  $I_{\rm DS}$  saturates. The maximum  $I_{\rm DS}$  is therefore defined by  $V_{\rm GS}$ .

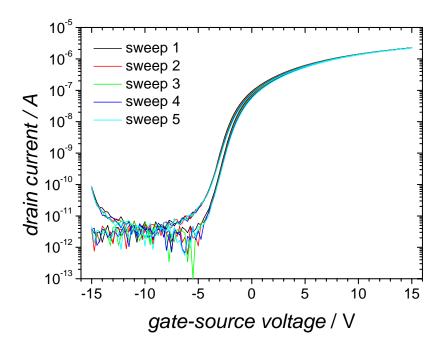

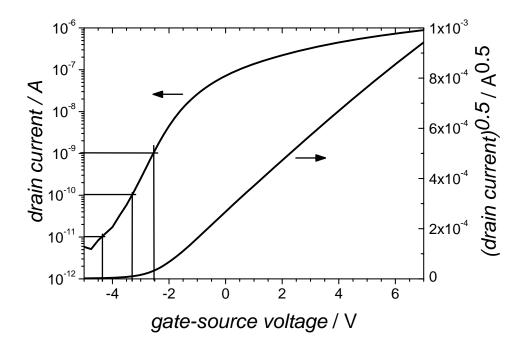

**Figure 3:** Transfer characteristics of dialysis grade PVA /  $C_{60}$  OFETs. Six successive measurements with slow sweep rates (70 mV / sec).  $V_{DS}$  is 10 V.

To measure a transfer characteristics  $V_{\rm GS}$  is sweeped while a constant  $V_{\rm DS}$  is applied (shown in Figure 3). Transfer characteristics can be measured in the linear (low  $V_{\rm DS}$ ) and in the saturation regime (high  $V_{\rm DS}$ ). A common model of field effect transistors [25] gives  $I_{DS}$  in the linear regime (at low  $V_{\rm DS}$ ) as:

$$I_{DS,lin} = \frac{W}{L} \mu_{FET} C_i \left( V_{GS} - V_{th} \right) V_{DS} \tag{1}$$

$I_{\rm DS}$  in the saturation regime (at high  $V_{\rm DS}$ ) is:

$$I_{DS,sat} = \frac{W}{2L} \mu_{FET} C_i \left( V_{GS} - V_{th} \right)^2 \tag{2}$$

These two equations are valid under the assumptions, that (i) the field along the channel is much lower than across it (gradual channel approximation) and (ii) that the mobility  $\mu_{\text{FET}}$  is constant [24].

W and L are the channel width and length, respectively.  $\mu_{FET}$  is the field-effect mobility (of the majority charge carriers),  $C_i$  the geometric capacitance of the dielectric,  $V_{GS}$  is the voltage

applied to the gate,  $V_{\rm DS}$  is the voltage applied to the drain (both  $V_{\rm GS}$  and  $V_{\rm DS}$  are defined versus the source potential, which is usually grounded) and  $V_{\rm th}$  is the threshold voltage, as will be explained later. The charge carrier mobility is calculated in either the saturation or in the linear regime from the above equations. The differential  $\partial I_{DS}/\partial V_{GS}$  is called the transconductance. In an ideal device, the mobilities calculated in the linear and saturation regime are the same and the mobility depends on the the charge carrier density which is defined by the applied  $V_{\rm GS}$ . Also the contact resistance ( $R_{\rm C}$ ) can influence the measured mobility [26]. The mobility in the linear regime is less affected by  $V_{\rm GS}$  and  $R_{\rm C}$ , therefore equation 1 is used in this work to determine the mobility, as is also done for MOSFETs [23]. The threshold voltage  $V_{\rm th}$  can be extracted by determining the x-axis intercept of ( $I_{\rm DS}$ )<sup>1/2</sup> versus  $V_{\rm GS}$  in the saturation regime [27], as shown in Figure 4, or by the maximum in a second derivation of  $I_{\rm DS}$  versus  $V_{\rm GS}$  at low drain voltage [28].  $V_{\rm th}$  is the voltage where the conducting channel is formed. In the accumulation mode  $V_{\rm th}$  is given by [29]:

$$V_{th} = \pm \frac{qn_0d}{C_i} + V_{fb} \tag{3}$$

where  $V_{\rm fb}$  is the flat-band potential which accounts for any work-function difference between the semiconductor and the gate metal, q is the elementary charge,  $n_0$  is the density of free carriers, and d is the thickness of the semiconductor. The sign of the right-hand side in the equation corresponds to the sign of the charge carriers [29]. From this equation a change in  $V_{\rm th}$  between the forward and the reverse scan and thereby a hysteresis can be expected, if: (i)  $n_0$  changes (e.g. due to trapping of free charge carriers), (ii)  $C_{\rm i}$  changes (e.g. charge injection from the gate into the dielectric or polarisation of the dielectric) and (iii)  $V_{\rm fb}$  changes (e.g. structural changes in the semiconductor).

The basic concept of an OFET is that of an electrical switch, that can turn a current on and off. The ratio between these two currents (the on/off ratio) is a measure for the performance of the OFET.

In general organic semiconductors are intrinsically nondoped and therefore non conducting without an applied gate field ("normally off"). Field effect transistors using nondoped organic semiconductors work in the accumulation mode (the gate field accumulates charges at the semiconductor / dielectric interface that form the channel).

From the log-plot of a transfer characteristics it is obvious that  $I_{\rm DS}$  starts to increase before  $V_{\rm th}$  is reached. This is the subthreshold regime. In Si transistors the "kink" where  $I_{\rm DS}$  starts to increase is called "turn on voltage" and describes the start of the inversion regime. As there exists no inversion in organic semiconductors the phrase "turn on voltage" can be misleading [30]. Alternatively, "switch on voltage" can be used to describe the "kink" in the logarithmic plot of the transfer characteristics where the current starts to increase [31]. The current increase in the subthreshold regime is measured as the subthreshold slope S (also called subthreshold swing), telling which additional  $V_{\rm GS}$  is necessary to increase  $I_{\rm DS}$  by a factor of ten (one decade (dec)). Values as low as about 100 mV/dec have been reported [32, 33], which is close to the theoretical limit of 60 mV/dec at RT [32, 34], which can be calculated from [25]

$$S = (\ln 10) \frac{dV_{GS}}{d(\ln I_{DS})} = (\ln 10) \frac{kT}{q} \left(\frac{C_i + C_D}{C_i}\right)$$

(4)

where  $C_D$  is the semiconductor depletion-layer capacitance.

**Figure 4:** Transfer characteristics at RT of a dialysis grade PVA /  $C_{60}$  OFET in the saturation regime indicating S in the log plot and the  $I_{DS}^{0.5}$  plot to extract  $V_{th}$ .  $V_{DS}$  is 10 V.

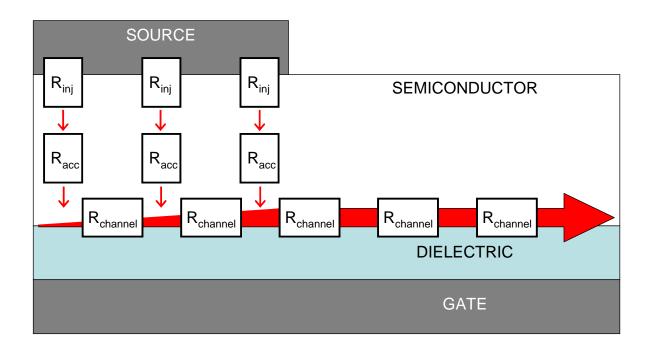

The extraction of  $V_{\rm th}$  and  $\mu_{\rm FET}$  is important, because a "good" OFET is defined having a low  $V_{\rm th}$  and a high  $\mu_{\rm FET}$ . A problem is that ohmic injecting and extracting contacts at source and drain, respectively, are assumed. The overall device resistance  $R_{\rm on}$  can be extracted from the linear regime of the output characteristics as the conductance  $\partial I_{DS}/\partial V_{DS}$ .  $R_{\rm on}$  is the sum of the resistances that influence  $I_{\rm DS}$ : charges are injected from the source  $(R_{\rm S})$ , traverse the device  $(R_{\rm channel})$  and are extracted at the drain  $(R_{\rm D})$ :

$$R_{on} = R_S + R_{channel} + R_D = R_C + R_{channel} \tag{5}$$

Ohmic contacts are defined such that  $R_{\text{channel}} >> R_{\text{C}}$  [12].  $R_{\text{channel}}$  scales with L, meaning that a short L causes a small  $R_{\text{channel}}$ . Therefore short channel OFETs are often contact limited. This is especially a problem for high speed OFETs, because the switching speed (the cut of frequency) scales with  $1/L^2$  [25, 34], making a short L necessary.

The reasons for non-ohmic contacts can be manifold [35]: Electrode surface contamination can increase  $R_{\rm C}$  and there is a difference between organic-on-metal and metal-on-organic interfaces. The resulting dipoles at the metal semiconductor interface can cause an increased  $R_{\rm C}$  [12, 35] and several models are used that can describe such organic / metal and organic / organic interfaces [36]. Methods to improve charge injection to overcome problems with  $R_{\rm C}$  have very recently been reviewed by Braga and Horowitz [23].

If there is a resistance to inject holes at the source, e.g., one might intuitively conclude that there is no contact resistance at the drain, because the energy levels are the same as at the source, but now holes are extracted from the semiconductor. Interestingly, measurements show that  $R_{\rm S}$  and  $R_{\rm D}$  are more or less equal and in general gate voltage dependent [12]. Therefore it can be concluded that  $R_{\rm C}$  is the sum of two resistances

$$R_C = R_{ini} + R_{acc} \tag{6}$$

where  $R_{\rm inj}$  is the injection resistance (due to non-Ohmic contacts) and  $R_{\rm acc}$  is the access resistance. In staggered geometries  $R_{\rm acc}$  can be caused by the thickness of the semiconductor layer: Injected charges have to move through this layer before they reach the channel (compare Figure 35). For coplanar geometries it has been shown that the resistance of the (usually) disordered organic semiconductor close to the metal contact is the limiting factor [12]. This  $R_{\rm acc}$  drastically reduces the mobility. It has been shown that a plasma treatment of Au electrodes improves the morphology of pentacene, which is grown onto Au S and D

electrodes. This improved morphology finally reduces  $R_{\rm acc}$  in the investigated coplanar OFET drastically and increases the mobility by 1 to 2 orders of magnitude [37].

A commonly used method to extract  $R_{\rm C}$  is the Transfer Line Method (TLM) [38]. A series of OFETs has to be built where all device parameters, except a decreasing L, are the same. After measuring  $R_{\rm on}$  of these transistors one can plot  $R_{\rm on}$  versus L. Under the assumption that  $R_{\rm channel}$  vanishes for very small L, one can extrapolate  $R_{\rm C} = R_{\rm on}$  (L=0). The TLM was introduced for a-Si TFTs [39].  $R_{\rm channel}$  decreases with increasing  $V_{\rm GS}$ , but also the value of the extracted  $R_{\rm C}$  depends on  $V_{\rm GS}$  [40, 41].

# 1.2. Hysteresis

In papers dealing with OFETs statements like "hysteresis must be avoided" or "only negligible hysteresis is observed" can be found frequently. Hysteresis is a bistability in the operational transistor current. It appears as a difference in the  $I_{DS}$  values observed during forward and backward sweeping of  $V_{GS}$ . As such it is not "per se" an unwanted feature, it could be useful in non-volatile memory devices, but it has to be avoided in standard integrated circuits.

*Brown* stated already in 1997 that "hysteresis is noticable by its absence in literature" [42]. Recently *Mijalkovic* declared, that for the modelling of OFETs and the corresponding circuit design, memory effects (bias stress effects and hysteresis) turned out to be the biggest challenge [43]. Threshold voltage shifts due to bias stress have been reported more frequently, but detailed investigations of hysteresis effects are rare and a complete picture of the physical background that may cause hysteresis in OFETs is still missing.

### 1.2.1. Examples from Inorganic Transistors

Some of the mechanisms causing hysteresis in OFETs are already quite well described in the literature on inorganic field effect transistor devices. Important hysteresis-related charge properties in silicon-silicon oxide MOS-FET transistors can be found also in OFETs, even if their description is generally more complex there. In Si-SiO<sub>2</sub> systems four general types of charges are known [44]:

- (i) Interface trapped charges (also called surface state, interface state or fast state) are defects or impurities at the interface that can be charged or discharged.

- (ii) Fixed charges in oxide is a positive charge due to structural defects close to the channel (2 nm) which does not communicate with the underlaying Si.

- (iii) Trapped charges in oxide are electrons or holes trapped in the bulk of the oxide. These traps can be introduced during device fabrication or charges (electrons or holes) are injected during device operation.

(iv) Mobile charges in oxide are mainly small alkali metal cations and H<sup>+</sup>, but can also be larger cations or anions, e.g. copper ions diffuse through germanium [45]. Flexodes (p-n junction devices with a variable *I-V* characteristics resulting from reversible Li<sup>+</sup> ion drift) were suggested in 1963 [46]. Mobile Na<sup>+</sup> ions in SiO<sub>2</sub> gate dielectrics cause threshold voltage shifts in MOSFETs [47].

The occurrence of charges (i) to (iv) in the Si-SiO<sub>2</sub> system is leading to hysteresis phenomena in inorganic transistor devices. Interestingly, the practical application of Si MOSFETs was delayed in the early 1960s because of severe gate bias instability problems caused by mobile ionic charges like Na<sup>+</sup>, Li<sup>+</sup>, K<sup>+</sup> and perhaps H<sup>+</sup> [44]. Water is known to diffuse into not densely packed SiO<sub>2</sub>. A small amount dissociates into H<sup>+</sup> and OH<sup>-</sup>. These ions can drift in an electric field to the channel and cause threshold voltage shifts [48].

Hysteresis phenomena have also been used as advantage in field effect devices with a polarizable gate. The first ferroelectric field effect memory resistor has been reported in 1963 [49] and the first field effect transistor with a ferroelectric gate in 1974 [50]. Problems in ferroelectric field effect memories (*e.g.* due to the depolarization field), investigated in detail by *Würfel et al.* [51, 52], caused companies to leave the field. The revival in the 90s [53] brought ferroelectric memories onto the market [54, 55].

In most other cases besides memory applications even small hysteresis is an unwanted effect. Its occurrence has been described in a number of publications. Hysteresis in a-Si TFTs increases with increasing temperature [56]. Leroux et al. report that high k dielectrics increase the number of traps and thereby the size of the hysteresis [57]. In the silicon transistor literature Fleetwood et al. suggested to distinguish between the physical location of the defects (oxide traps, border traps and interface traps) and how such defects respond during the measurement [58]. Powell termed the effects due to reversible trapping "dynamic  $V_{th}$  shift" and the degradation effect " $V_{th}$  instability" [59]. For references on bias stress effects in a-Si investigated during two decades see Ref. [60].

# 1.2.2. Hysteresis in OFETs

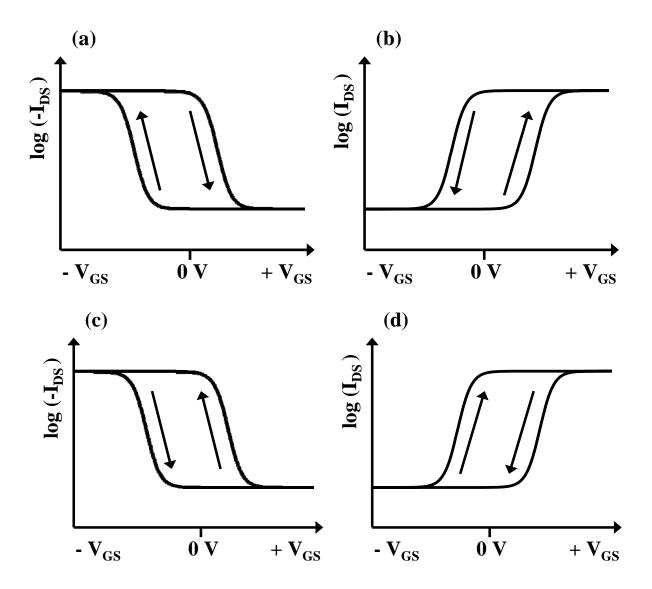

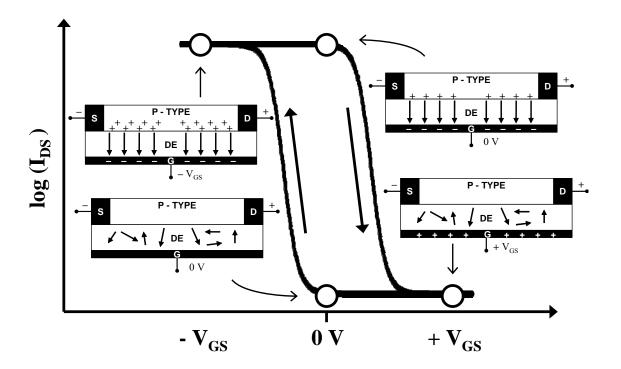

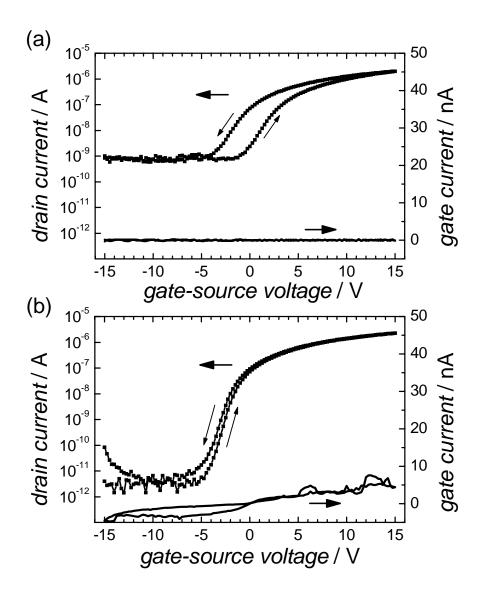

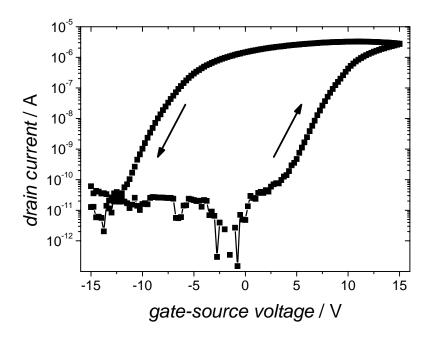

Cyclic transfer characteristics ( $I_{DS}$  vs  $V_{GS}$ ) where  $I_{DS}$  depends on the sweep direction of  $V_{GS}$  are called to show a "hysteresis", as schematically depicted in Figure 5. These reversible electrical bistabilities are frequently observed in organic field effect transistors. Depending on

the microscopic effect the hysteresis can result in a back sweep current (the sweep from on to off) that is either higher or lower than the forward sweep current (the sweep from off to on). A hysteresis is sometimes called "clockwise" or "anti-clockwise". However, these notations can be misleading, because the direction of the hysteresis also depends on the p- or n-type character of the investigated OFET, as demonstrated in Figure 5:

**Figure 5:** Schematic transfer characteristics ( $I_{DS}$  versus  $V_{GS}$ ) of p-type (a), (c) and of n-type (b), (d) OFETs. (a) and (b) show higher BSC hysteresis. For p-type OFETs (a) this higher BSC hysteresis turns "clockwise" whereas for n-type OFETs (b) this hysteresis turns "counterclockwise". (c) and (d) show lower BSC hysteresis. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

Figure 5 (a) and (b) show schematic transfer characteristics where the back sweep current is higher than the forward sweep current. For p-type OFETs the direction of this hysteresis is "clockwise" whereas for n-type OFETs the turning direction is "anti-clockwise". Figure 5 (c) and (d) show schematic transfer characteristics where the back sweep current is lower than the forward sweep current. To avoid ambiguities, the notation higher back sweep current hysteresis (higher BSC hysteresis) or lower BSC hysteresis is used in this paper. Lower BSC hysteresis is very often attributed to charge carrier trapping close to the channel, whereas higher BSC hysteresis is usually caused by mobile ions in the dielectric or by (ferroelectric-) polarization of the dielectric.

Threshold voltage shifts are frequently reported in literature due to bias stress [61, 62, 63]. Bias stress is the application of a (usually) constant  $V_{\rm GS}$  for an extended time. Such bias stress causes instabilities which may lead either to hysteresis, if the bias stress effect occurs to a large extent reversibly with  $V_{\rm GS}$ , or to degradation, if the bias stress effect is irreversible. Hysteresis and degradation might have the same physical origin [64]. The direction of the shift is such that a fully turned on OFET slowly turns itself off and vice versa [63, 65]. Recovery is sometimes possible; it follows a power law time dependence and may take a few days in the dark [63]. Investigating the threshold voltage shift under illumination suggests that traps at the interface may be responsible for the observed shift [65, 66, 67].

Bias stress in an OFET can also cause a change in effective field effect mobility, which is attributed to an irreversible structural change in the semiconductor due to the electrostrictive effect [68]. The change is independent on the trapping and detrapping of mobile charge carriers caused by bias stress. Such electric field induced mechanical strains are also discussed as failure mode in inorganic high-electron mobility transistors [69].

#### 1.2.2.1. Measuring hysteresis

For the characterisation of organic transistors and materials, a collection of IEEE Standard Test Methods has been published [30]. In this standard it is recommended to measure the forward and the reverse sweep to make sure that no hysteresis is present to prevent wrong calculations of OFET parameters. However, currently there is no generally accepted procedure how to measure hysteresis in OFETs.

The hysteresis can be characterized by the transfer characteristics of OFETs or by capacitance-voltage (C(V)) characteristics of corresponding metal-insulator-semiconductor

(MIS) structures. C(V) characteristics are used to distinguish between p- and n-type semiconductors: The depletion layer acts as a capacitance in series to the dielectric changing the total capacitance, so a high capacitance is measured in the accumulation regime. In this paper, hysteresis effects are discussed mainly by evaluating the transfer characteristics of OFETs.

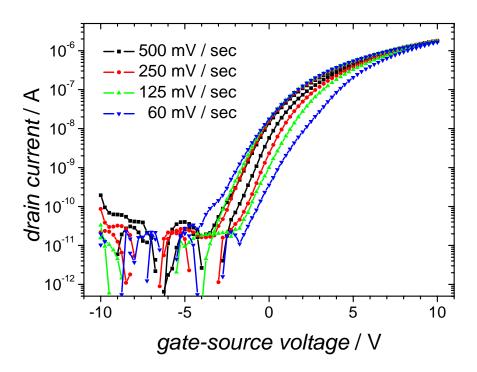

As shown above, the hysteresis can be interpreted as a shift of the threshold voltage depending on the gate voltage sweep direction. Therefore a simple definition of  $V_{th}$  in an OFET with hysteresis cannot be given. Both values, the  $V_{th}$  in the off-to-on sweep and the  $V_{th}$  in the on-to-off sweep and the size of the hysteresis often depend on the sweep rate, the starting and end voltage of the sweep, the step width, the delay time, the hold time and the step delay time [70]. A comparison of different devices is therefore difficult or impossible, if these parameters are not given.

Hysteresis due to reversible effects can only be seen in the transfer characteristics when changing the sign of  $V_{GS}$  during the measurement, preferentially with a symmetric sweep around  $V_{GS} = 0$  V (e.g. sweep  $-V_{GS}$  to  $+V_{GS}$  and back). Otherwise, without changing the sign of  $V_{GS}$ , the measurement may only reveal degradation due to bias stress effects.

Reversible hysteresis effects as described in this article cannot be measured with output characteristics ( $I_{DS}$  versus  $V_{DS}$ ) [71]. During such a measurement  $V_{GS}$  is changed in steps from  $V_{th}$  (ideally 0 V) to the on-state (e.g. +  $V_{GS}$  for n-type OFETs). The sign of the applied  $V_{GS}$  usually does not change during an output measurement. If differences between the forward and the backward scan are observed in the output characteristics this reflects in most cases a continuous increase or decrease of  $I_{DS}$  due to bias stress.

The pulsed measurement method [66, 72, 73] is a way to measure hysteresis-free characteristics of OFETs even if the OFET would normally show hysteresis: The idea of the gate pulse method is to apply off-voltage (depletion voltage) to the device under test after each measurement point. The measurement voltage ( $V_x$ ) is applied for a certain short time. At the end of the pulse  $I_{DS}$  is measured, followed by the application of the off voltage for a longer period. During this long off-pulse the changes due to the measurement pulse (polarization, (de-)trapping, ...) are usually reversed. This procedure is repeated for each step. OFET characteristics measured with this pulse method do not show hysteresis, if the pulse lengths are chosen properly. However such investigated OFETs may show hysteretic characteristics in a normal sweep measurement of the transfer characteristics. Though the

pulsed method may be used for obtaining device parameters like mobilities, it should be accompanied by conventional symmetric sweeps with different sweep rates to rule out memory effects.

#### 1.2.2.2. Quantifying Hysteresis

Several quantifications for the magnitude of the hysteresis were suggested: Half width at mid capacitance [74], the maximum gate voltage shift at a given  $I_{DS}$  [75], or the average  $I_{DS}$  for a given  $V_{GS}$  [76]. Quantifying the hysteresis as a shift of  $V_{th}$  for a given sweep rate may be also a measure to compare different devices. Hysteresis phenomena are based on dynamic processes depending heavily on the time of the measurement and on the duration of the applied voltage. These parameters can change the size of the hysteresis and also the slope of the curves. Therefore strict rules (e.g. a refined IEEE standard [30]) may be useful to ensure a comparable quantification.

# 1.2.3. Hysteresis mechanisms

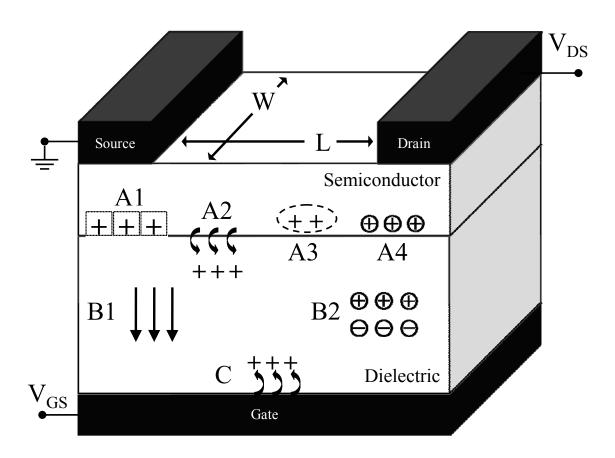

Many physical effects causing hysteresis in OFETs are mentioned in the literature. Some of these effects are identical to those already explained for inorganic transistors. Given the complex nature of hysteresis in OFETs, the underlying effects, as shown in Figure 6, can be grouped related to the location within the device where the effect acts [77]:

- o Effects of mobile charges close to or in the *semiconductor channel* (near the semiconductor / dielectric interface): A1) Trapped majority or minority charges in the channel close to the semiconductor / dielectric interface, A2) Charge injection from the semiconductor into the dielectric, A3) Slow reactions (*e.g.* bipolaron formation) of mobile charge carriers in the polymeric semiconductor and A4) mobile ions in the semiconductor

- Effects resulting in a bulk polarization of the gate dielectric: B1) polarisation of the dielectric (ferroelectrics as dielectric or metastable "quasi-ferroelectric" polarization in the dielectric) and B2) mobile ions in the dielectric

- o Charge injection from the gate electrode into the dielectric

How to distinguish between different mechanisms? The most obvious difference is the direction of the hysteresis: Charge injection from the semiconductor into the dielectric, for example, causes lower BSC hysteresis, whereas polarization of the dielectric causes higher

BSC hysteresis. If the direction is the same, investigating the sweep rate dependence can clarify which type of hysteresis is present, because different hysteresis mechanisms have different sweep rate dependences [44]. Mobile ions in the dielectric, *e.g.*, move slowly, therefore slow sweep rates can cause a large hysteresis, whereas fast sweep rates reduce the size of this hysteresis. Charges injected from the gate into the dielectric (trap like injection) cause the opposite effect: Metastable shallow traps can only cause a hysteresis when the sweep rate is faster than the lifetime of the trapped charge carrier. Such different dependences on the sweep rate can be used to determine which hysteresis mechanism is dominant in a device.

The reported mechanisms are schematically categorized and summarized in Figure 6:

**Figure 6:** Scheme of a staggered bottom gate OFET illustrating the described mechanisms causing hysteresis. A detailed description of the mechanisms can be found in the text. In general, each effect is independent of the sign of the charge. For simplicity only one type of charge is shown in the figure. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

#### 1.2.3.1. Trapped majority or minority charges at the channel

Traps at the semiconductor / dielectric interface can cause lower BSC hysteresis. There are various traps in organic layers such as impurities, structural defects (e.g. the effective conjugation length of a polymer can slightly change its HOMO – LUMO levels) and self trapping (the charge creates a polarization of its surrounding which again stabilizes the position of the charge) [65, 78, 79]. If the release rate of charges out of such a trap is sufficiently low, the sweep rate may be faster than the time necessary to reach thermal equilibrium, which results in hysteresis effects in the electric characteristics of the device [79].

Various material combinations show lower BSC hysteresis due to traps [75], examples are pentacene transistors on thermally grown SiO<sub>2</sub> [80] as well as on sol-gel cast SiO<sub>2</sub> [81], pentacene on various organic dielectrics [82] or C<sub>60</sub> on a triple layer of SiO<sub>2</sub> / zirconium-silicon oxide / SiO<sub>2</sub> [83]. Oxygen or water can influence such trap caused hysteresis [42, 84, 85, 86, 87, 88] and oxygen or water can also change the bias stress effect [89, 90, 91, 92, 93]. OH groups are presumed to act as electron traps [94, 95, 96]. Self assembled monolayers (SAMs) [83, 94, 97, 98] and dielectrics without OH groups [99] are known to reduce these traps and change the mobility [100, 101, 102]. In ambipolar OFETs, hysteresis due to charge carrier trapping is frequently observed. [72, 103, 104, 105, 106, 107]

Dielectrics with low k values ("low k dielectrics") increase the mobility and reduce the hysteresis [16, 108, 109, 110]. High k dielectrics covered with a thin flat layer of a low k dielectric result in OFETs with low voltage and high mobility [33, 111], whereas a rough interface causes additional traps resulting in increased hysteresis [112, 113].

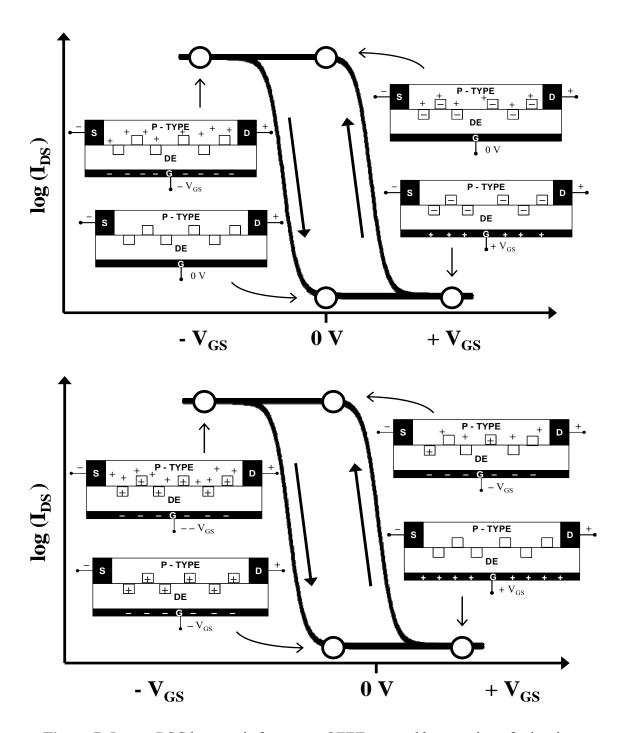

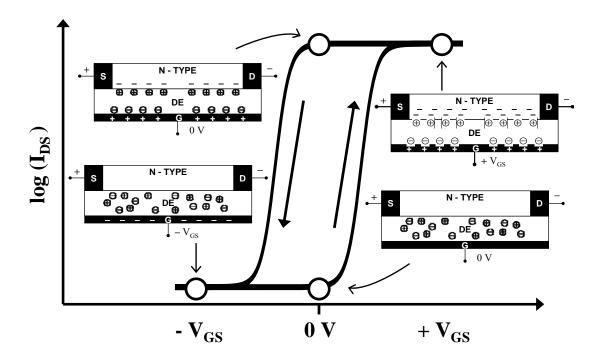

Both types of charge carriers (holes and electrons) can be trapped (as shown by modelling and second harmonic generation measurements [114, 115]). For a p-type semiconductor holes are the majority carriers and electrons are the minority carriers. Trapping of majority and minority carriers both cause lower BSC hysteresis, as schematically shown in Figure 7:

Figure 7: Lower BSC hysteresis for p-type OFETs caused by trapping of minority charge carriers (top) or caused by trapping of majority charge carriers (bottom). The circles indicate the situation of the respective cartoon. Meaning of the symbols: □ empty trap, ⊞ trapped hole, □ trapped electron, ⊕ cation, ⊖ anion, + hole, − electron, S source, D drain, G gate, DE dielectric, → dipole orientation. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

#### 1.2.3.1.1. Minority Traps

Long lifetime minority traps (e.g. electron traps in pentacene) that fill fast and empty slowly can cause hysteresis, as shown in Figure 7. For pentacene on SiO<sub>2</sub> long lifetime deep electron traps are suggested [60, 88, 116]. When starting the sweep in the on-state (negative  $V_{GS}$  for pentacene) all electron traps are empty. Upon applying an off voltage (positive  $V_{GS}$ ), the traps are quickly filled. When sweeping fast from off-to-on, the negatively charged traps induce more (mobile) positive charges than corresponding to the given  $V_{GS}$  field. These excess holes cause higher  $I_{DS}$  in the forward sweep. In the on-state all traps are emptied causing lower  $I_{DS}$  in the back sweep. The faster the forward sweep, the more traps are still filled and the higher is  $I_{DS}$ . This explains why the size of this hysteresis increases for fast sweeps.

Gu et al. discuss whether negative or positive charges are trapped in pentacene / octadecyltrichlorosilane / SiO<sub>2</sub> OFETs [116]. They conclude that stored negative charges, most likely electrons, in pentacene dominate the observed shift in  $V_{\rm th}$ . The first hint to this conclusion was given by comparing the different sweep directions in the transfer characteristics for high negative  $V_{GS}$ : Sweeping in the off-to-on direction, the electron traps are slowly emptied, causing a  $V_{GS}$ -dependent mobility and non-linear transfer characteristics. During the on-to-off sweep the electron traps are already empty. For negative  $V_{\rm GS}$  this does not change and therefore  $I_{\rm DS}$  versus  $V_{\rm GS}$  is linear. To confirm this mechanism, time domain measurements were performed. First a predefined starting voltage  $V_{\rm GS0}$  was applied. After quickly changing to  $V_{\rm GS}$  = -20 V the change in  $I_{\rm DS}$  with time (at fixed  $V_{\rm GS}$  = -20 V and  $V_{\rm DS}$  = -10 V) was monitored. Depending on the applied voltages  $V_{\rm GSO}$  (before the measurement)  $I_{DS}$  was either constant or decreased with time. If electron acceptor states dominate the observed effect, these states are initially filled when a positive gate voltage  $V_{\rm GSO}$ is applied. The trapped electron population slowly decays by detrapping after  $V_{\rm GS}$  is switched from positive  $V_{\rm GS0}$  to -20 V. In the same manner  $I_{\rm DS}$  decays, since the decaying trapped electron population results in a decaying extra hole population that balances it. Accordingly, when starting with a more negative  $V_{GSO}$  (e.g. -50 V), all traps are emptied. After switching to -20 V still all traps are empty and no change in  $I_{\rm DS}$  vs time due to slow detrapping is expected. If hole traps cause the observed hysteresis, the opposite behaviour is expected [60, 88, 116]. Also scanning Kelvin-probe microscopy can show which type of charge carriers are trapped at the channel [117].

#### 1.2.3.1.2. Majority Traps

Also majority traps (e.g. hole traps in pentacene) that fill fast and empty slowly can cause a lower BSC hysteresis, as shown in Figure 7. When starting the scan from the off-state, the traps are empty. During the off-to-on sweep, the traps get filled. E.g. for pentacene OFETs, a certain number of field induced holes correspond to each negative  $V_{GS}$ . Some of the holes are quickly trapped. During the on-to-off sweep the trapped holes are slowly released (much slower than the sweep rate), therefore less mobile holes are in the channel at a given  $V_{GS}$  and the resulting  $I_{DS}$  is lower [60, 116]. The release rate of the traps must be slower than the scan rate, meaning that fast sweeps show larger hysteresis than slow sweeps. This dependence on the scan rate is important to distinguish between different hysteresis mechanisms.

From measurements on pentacene / SiO<sub>2</sub> OFETs it has been concluded that trapped holes (majority charge carriers) cause the hysteresis. An eqivalent circuit PSpice model has been developed which is able to simulate the observed hysteresis and the observed time dependence assuming trapped holes [118, 119].

Investigations on four n-type and two p-type semiconductors, each on four different substrates, show various trapping-type hysteresis effects [75]. However, the hysteresis could not be directly correlated to a certain dielectric or to a certain semiconductor. Trap caused hysteresis in OFETs is determined by the semiconductor / dielectric material combination and not by just one material (semiconductor or dielectric) alone.

Bias stress effects and hysteresis are closely related [71]. Deep and shallow traps at the interface of the dielectric with the semiconductor (e.g. pentacene on SiO<sub>2</sub>) are emptied on different time scales: Shallow traps are emptied fast causing hysteresis, whereas deep traps emptied on a much longer time scale (e.g. hours) cause a shift in  $V_{th}$  known as bias stress effect [70, 71].

# 1.2.3.2. Charge injection from the semiconductor into the dielectric

This mechanism is very similar to the charge trapping mechanism. The only difference is the location of the "traps": Charges are injected from the semiconductor into the dielectric. From the device point of view these injected charges can also be seen as traps that cause lower BSC hysteresis [120, 121, 122, 123]. *Katz et al.* proposed electrets that show reversible hysteresis due to charge injection as memories [124]. *Baeg et al.* put a chargeable electret (*e.g.* poly( $\alpha$ -

methylstyrene) (P $\alpha$ MS)) between the SiO<sub>2</sub> dielectric and the pentacene to build a memory device. A critical voltage is needed to switch the device. Characterising the OFET with voltages below this critical switching voltage results in hysteresis free characteristics [125, 126].

Charge injection from the semiconductor into the dielectric is very similar to floating gate memory transistors, where an additional metal layer (the floating gate) is inserted into the dielectric [127]. Floating gate transistors are well known in inorganic technology [25]. The injected charges are quasi permanently stored in the floating metal layer and influence the gate field. This additional polarization contributing to the gate field can be seen as a change of the threshold voltage of the transistor. Floating gate OFETs have a certain threshold voltage that is necessary to inject charges into the floating gate. An ideal floating gate shows no hysteresis measuring the transfer characteristics below this threshold, whereas cyclic sweeps above this threshold show hysteresis. Only recently floating gate OFETs [120] and all organic floating gate OFETs [128] have been demonstrated [127].

#### 1.2.3.3. Slow reactions of mobile charge carriers

In general lower BSC hysteresis is attributed to trapping of charge carriers (A1), but there are examples which contradict the trapping mechanism: Reducing the sweep rate (slower measurements) caused an increase of the hysteresis, pointing to species with low mobility. Measuring at increased temperature increases the hysteresis and also shifts the curves. Ions (*e.g.* iodine) influence this hysteresis, but the complexity suggests that a second mechanism is present in the device [129, 130]. Simulations show that traps cannot explain the observed hysteresis [131]. As the subthreshold slope is closely related to interface traps [31, 114, 132], hysteresis in OFETs with high subthreshold slope cannot be explained by traps [34].

A polaronic/bipolaronic mechanism has been suggested to explain these observed lower BSC hysteresis in OFETs using conjugated polymers [133, 134, 135]. In the on-state of an OFET a high charge carrier density is induced in the semiconductor close to the dielectric interface. Charge carriers in conjugated polymers can be described as polarons or bipolarons. It is suggested that due to the very high polaron density some polarons overcome the coulomb repulsion and form double charged bipolarons. If mobile counterions (*e.g.* charged impurities) are present, these might stabilize the polaron or bipolaron due to neutralization of their charge. Different properties of polarons and bipolarons, their slow formation and

complexation with counterions might cause lower BSC hysteresis [133, 135, 136, 137, 138]. Theoretical predictions have been presented and verified experimentally [134, 139].

It has to be mentioned that there is still an ongoing discussion in literature whether bipolarons do exist or not in organic semiconductors. All the theoretical conciderations can be explained by a polaron-polaron complex formation other than bipolarons, e.g. a dimerisation [140]. This dimerisation would lead to  $\sigma$ -bonds that should be detectable.

#### 1.2.3.4. Mobile ions in the semiconductor

Ions in the semiconductor can also cause lower BSC hysteresis. This is the opposite effect than mobile ions in the dielectric would cause. Mobile ions in the semiconductor that have the same polarity as majority carriers move slowly to the channel. As the total number of charges at the channel is fixed (determined by the applied voltages and the device parameters), ions reduce the number of mobile charges at the channel. This mechanism also decreases the  $I_{DS}$  causing lower BSC hysteresis [141]. As ions move slowly, this hysteresis is expected to be larger for slower sweep rates, which gives the opportunity to distinguish between traps and mobile ions. In principle, also ions in the semiconductor with opposite sign to majority charge carriers could cause lower BSC hysteresis (majority and minority traps both cause lower BSC hysteresis), but no example in the literature could be found.

Li ions diffuse in and out of the depletion layer of a poly(3-hexylthiophene (P3HT) / Al Schottky contact causing a stable hysteresis in the *I-V* characteristics of the diode. The polymer layer is mixed with ethylene carbonate, a plasticizer that is known [142, 143] to increase the mobility of inorganic ions [144]. Mobile Na<sup>+</sup> ions diffuse under the influence of an applied voltage from a substrate underneath into an organic semiconductor where the ions cause hysteresis in the *I-V* characteristics [145]. Nanotube based OFETs coated with a layer containing Na<sup>+</sup> ions show lower BSC hysteresis, because the ions can diffuse to the channel and thereby decrease the "on" current. The authors observed that humidity increases the hysteresis while evacuating the device drastically decreases the hysteresis [141].

#### 1.2.3.5. Polarisation of the dielectric

#### 1.2.3.5.1. Ferroelectrics as dielectric

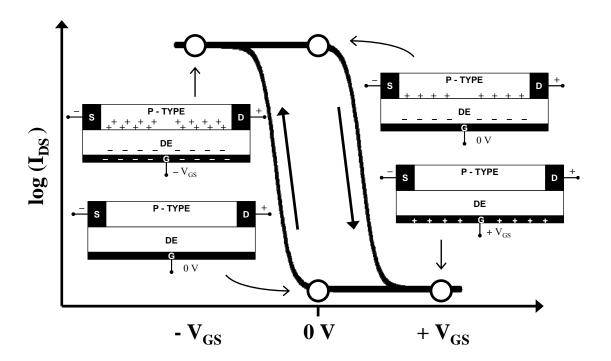

Ferroelectric dielectrics are materials that show a remanent polarisation due to an externally applied electric field. This remanent polarisation causes an electric field in addition to the gate field, therefore ferroelectric dielectrics cause higher BSC hysteresis, as shown in Figure 8:

**Figure 8:** Higher BSC Hysteresis for p-type OFETs caused by (ferroelectric) polarization. For a guide to the symbols see the caption of Figure 7. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

A coercive voltage has to be applied to reduce the polarization (the charge displacement) to zero. This transition voltage scales with the thickness of the ferroelectric: the thicker the layer, the higher the coercive voltage [146]. The hysteresis loop saturates when the whole material is polarized [147].

In general a ferroelectric material placed between two electrodes (metal-insulator-metal (MIM) structure) can be polarized in both directions, only depending on the applied field. The strong electric field of the remanent polarisation is stabilized by neutralizing charges in the metal electrodes, which reduce the depolarizing field [51, 52, 148]. In a metal-insulator-

semiconductor (MIS) structure this can be different: In general only one type of charge carrier is mobile in an organic semiconductor, therefore the ferroelectric can be polarized only in one direction, as shown in Figure 8. Higher BSC hysteresis due to ferroelectric gate dielectrics seems promising for memory elements, but problems with long term stability of the induced polarisation, a known problem for inorganic ferroelectrics, have not been addressed yet.

The first ferroelectric OFET (FerrOFET) using an inorganic ferroelectric has been demonstrated in 2001 [149]. Other materials [150] and the first all-organic FerrOFET followed [151, 152]. The material used by *Schroeder* is not strictly ferroelectric, but ferroelectric-like with molecular dipoles that are quasipermanently oriented in an external electric field. Devices have been improved [153] and a solution processed FerrOFET using poly(vinylidene fluoride/trifluoroethylene) P(VDF/TrFE)) as organic ferroelectric insulator and poly[2-methoxy,5-(2'-ethyl-hexyloxy)-p-phenylene-vinylene] (MEH-PPV) as organic semiconductor has been demostrated [154]. The annealing temperature of P(VDF/TrFE) is 140°C, which makes it compatible to processing on organic substrates. The on-off ratio after a week (programming once and reading the data for a week) was still 10<sup>4</sup>. The required programming time to achieve an on-off ratio of 10<sup>3</sup> was 0.5 ms [154]. Similar results were obtained for p-type and n-type FerrOFETs using P(VDF/TrFE) as ferroelectric insulator and MEH-PPV and PCBM as semiconductor, respectively [155]. Further improved devices [146, 156, 157], ambipolar FerrOFETs [158] and FerrOFET arrays [159] have been demonstrated, but products using FerrOFETs as memory element are not yet on the market [127].

#### 1.2.3.5.2. "Quasi-ferroelectric" polarisation of the dielectric

If the dielectric contains polar groups (*e.g.* polar side groups, short polymer chains, residual solvent) that can slowly move or reorient due to an external electric field, these dielectrics cause an effect very similar to ferroelectric materials, therefore often called "quasiferroelectric" (in ferroelectric materials the polarisation is a thermodynamically stable state). Slow metastable polarisation of the dielectric also causes higher BSC hysteresis [60, 124] as shown in Figure 8.

Poly(vinyl phenol) (PVP) is known to cause hysteresis due to polarisation in the dielectric, resulting in higher BSC hysteresis [160]. As this is an effect due to mobile dipoles in the bulk, the size of the hysteresis scales with the thickness of the PVP layer [77]. Furthermore the size of the hysteresis heavily depends on the sweep rate, showing larger hysteresis for slower

sweep rates [161]. In addition, the water content, especially when working under ambient conditions, influences the hysteresis [74]. The size of the hysteresis can be decreased or even removed by thermally cross linking the PVP [77, 80, 161, 162]. However different cross linking procedures may have different effects on the hysteresis: extended cross linking time or reducing the amount of volatile species by vacuum treatment reduce the hysteresis, whereas UV exposure causes an increase in hysteresis [161].

Other materials than PVP, even without polarising dipoles, can be electrostatically charged during device fabrication to influence the device properties. In the case, when the charging is not changed during device operation, the OFET shows no hysteresis, whereas if standard device operation changes the charging of the dielectric, hysteresis may be observed [163].

#### 1.2.3.6. Mobile ions in the dielectric

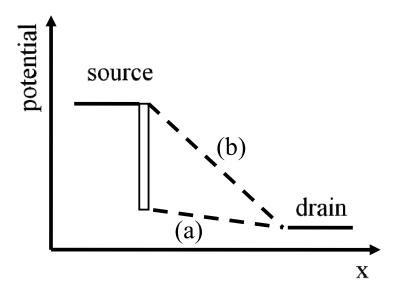

Mobile ions in the dielectric also cause higher BSC hysteresis. The effect in the device is very similar to polarization of the dielectric (Figure 8), as can be seen from Figure 9, schematically showing higher BSC hysteresis due to mobile ions in the dielectric for a n-type OFET.

**Figure 9:** Higher BSC hysteresis for n-type OFETs caused by mobile ions in the dielectric. For a guide to the symbols see the caption of Figure 7. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

Applying an "on" voltage (in this case a positive  $V_{\rm GS}$ ) to the gate, the cations move towards the semiconductor. When  $V_{\rm GS}$  is sweeped back to 0 V (backward sweep) the ions stay close to the semiconductor, thereby retaining the diminishing field and causing higher BSC hysteresis [164]. More ions accumulate close to the semiconductor when the on-voltage is applied for longer time, therefore hysteresis phenomena increase with decreasing sweep rate.

As already pointed out, ions are known to cause threshold voltage shifts in inorganic transistors [45, 46, 47]. In general ions are at least as mobile in organic materials as in SiO<sub>2</sub>, therefore it is expected that they cause even more pronounced effects in organic materials: Ions in PMMA [165], in cyanoethylpullulane [16, 166] and in desoxyribonucleic acid (DNA) [167, 168] are proposed to cause the observed hysteresis. Na<sup>+</sup> ions diffusing from soda lime glass into the dielectric cause higher BSC hysteresis [161]. Water influences the ionic hysteresis in devices using poly(vinylcinnamate) / poly(vinylidene-fluoride/tetrafluoroethylene/hexafluoropropylene) double layers [111] or PVP [169] as dielectrics.

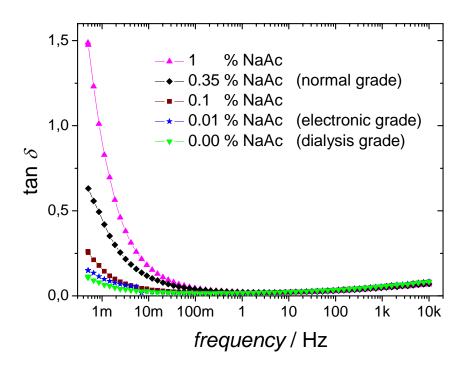

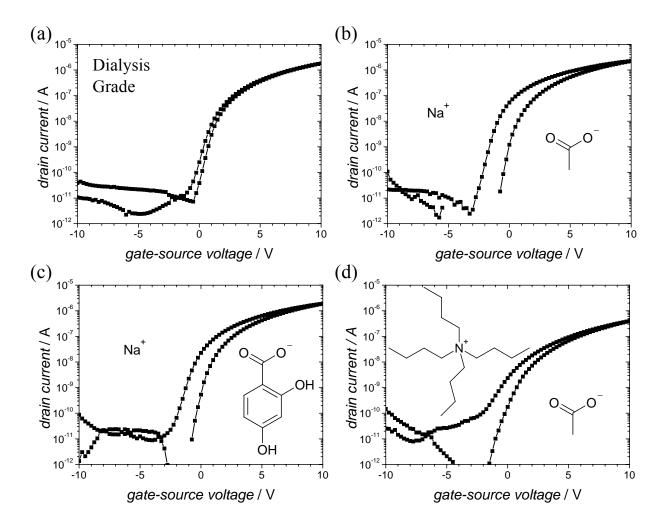

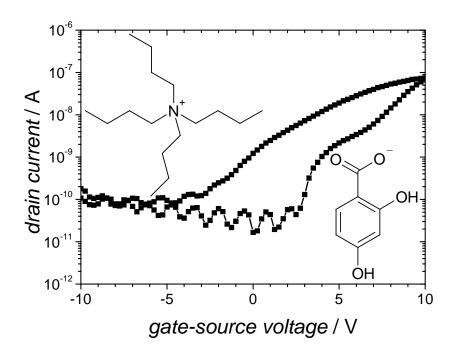

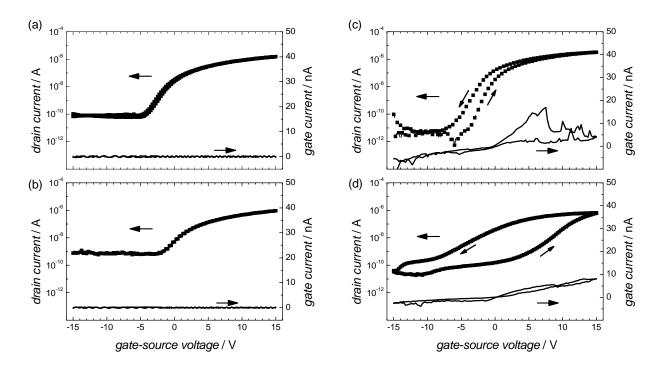

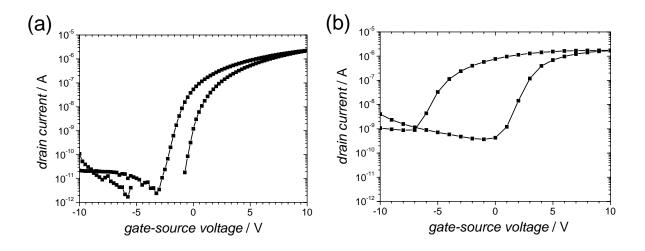

Typical dielectrics with mobile ions are polyelectrolytes. They are expected to reduce the operation voltage of OFETs due to their strong polarizability, but these OFETs show higher BSC hysteresis [170]. Detailed investigations of OFETs with poly(vinyl alcohol) (PVA) as dielectric and methanofullerene [6,6]-phenyl C61-butyricacidmethylester (PCBM) [171, 172] or MDMO-PPV [106] as semiconductors showed pronounced hysteresis in the transfer characterisitics. The hysteresis decreased with decreasing temperature, indicating that mobile ions are the reason for the hysteresis [173]. The situation is even more complex when ambipolar charge transport processes are investigated. Hysteresis effects from mobile ions have been observed in addition to ambipolar charge transport [174]. Detailed investigations on hysteresis in PVA based OFETs due to ions in the PVA will be discussed in section 3.1.1 of this dissertation.

It has been reported very recently, that mobile Na<sup>+</sup> in PVA may be the reason for the observed n-type transport in PVA / Pentacene OFETs [175]. It was known that the n-type transport is only observed after a thermal treatment of the finished OFET [174]. During the thermal treatment Na<sup>+</sup> ions diffuse from the PVA through the pentacene to the Au / pentacene interface. There these ions change the energy levels and enable electron injection.

For most applications mobile ions have to be avoided in organic integrated circuits to minimize device instability. However, immobilized ions at the semiconductor / metal interface can improve charge injection [176]. Electroluminescence and photovoltaic effect in

ionic junctions have been demonstrated [177], and recently nanoionic resistive switching for memory application has been reviewed [178].

#### 1.2.3.7. charge injection from the gate

If charges can be injected from the gate electrode into the dielectric these charges also cause higher BSC hysteresis. This mechanism is shown in Figure 10 for a p-type semiconductor and for electrons injected from the gate into the dielectric.

**Figure 10:** Charge injection from the gate into the dielectric causing higher BSC hysteresis in p-type OFETs. For a guide to the symbols see the caption of Figure 7. Reproduced with kind permission from Springer Science+Business Media: Ref. [21].

In the on-state (negative  $V_{\rm GS}$ ) electrons are injected from the gate into the dielectric. Upon reducing  $V_{\rm GS}$  to 0 V, the electrons stay in the dielectric thereby stabilizing the accumulated holes forming the channel. In most cases the electrons stay only for a short time, therefore fast sweep rates cause large hysteresis whereas slower sweep rates decrease the higher BSC hysteresis [179]. The size of the hysteresis also strongly depends on the maximum gate voltage. Inserting a blocking layer between the gate electrode and the dielectric reduces the observed hysteresis [77, 169, 179, 180, 181].

Usually, floating gate transistors use charge injection from the semiconductor into the dielectric [25, 127] (compare mechanism A2), but in some transistor systems it is also possible to inject charges from the gate to the floating gate [182, 183].

#### 1.2.3.8. Combined mechanisms

Using zirconium-silicon oxide as gate insulator, electrons can be injected from the semiconductor into the dielectric causing lower BSC hysteresis, or electrons can be injected from the gate into the dielectric causing higher BSC hysteresis [184]. In addition, the solvent used for casting the semiconductor can drastically influence the size of the hysteresis [185]. The strongest effect determines the direction and the size of the hysteresis, if more than one hysteresis mechanism is present [77]. It has been suggested to neutralize one hysteresis by an additional effect causing hysteresis in the other direction. Experimentally, the total hysteresis was reduced by balancing the effects [186]. However, problems with long term stability of the device operation will most probably occur.

# 1.3. Dielectric Spectroscopy

#### 1.3.1. MIM structures

The main focus discussing the characteristics of OFETs is usually on the semiconductor and its properties. Ongoing research showed that the dielectric has major influences on the device properties: The necessary voltage to form the channel is determined by the capacitance of the dielectric. Traps, dipoles and the surface roughness of the dielectric have a strong influence on OFET performances. Furthermore, the dielectric can influence the morphology of the semiconductor. Therefore electrical characterisations of the dielectric are becoming more and more important [187, 188, 189].

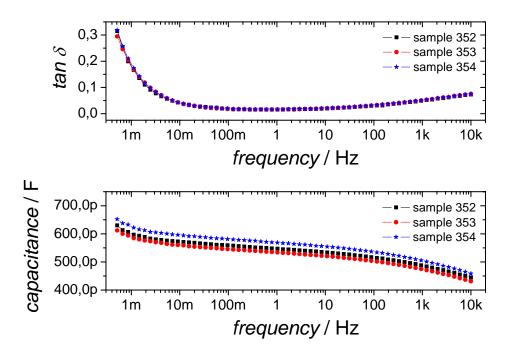

Dielectric spectroscopy is a powerful tool to investigate the electronic properties of insulating materials (dielectrics) [190, 191]. Dielectric spectroscopy measures the real and the imaginary part of the capacitance at various frequencies. The device geometry influences the capacitance, as can be seen from

$$C^* = \varepsilon^* \varepsilon_0 \frac{A}{d} = (\varepsilon' - i\varepsilon'') \varepsilon_0 \frac{A}{d} = \varepsilon' \varepsilon_0 \frac{A}{d} - i\varepsilon'' \varepsilon_0 \frac{A}{d} = C' - iC''$$

(7)

where  $C^*$  is the complex geometric capacitance,  $\varepsilon^*$  is the complex relative static permittivity (the "dielectric constant") of the dielectric,  $\varepsilon_0$  is the permittivity of free space ( $\varepsilon_0 = 8.854 \times 10^{-12} \text{ F/m}$ ), A is the area of the overlapping electrodes and d is the thickness of the dielectric. The real part (C' and  $\varepsilon'$ ) represents the capacity and is directly related to the polarization of the material, whereas the imaginary part (C'' and  $\varepsilon''$ ) represents the dielectric loss.

At sufficiently low frequencies any polar species (dipols, ions, etc.) can move and follow the changing electric field. This movement consumes energy and is therefore described by a loss mechanism. The dielectric loss angle ( $\tan \delta$ ), defined as

$$\tan \delta = \frac{C''}{C'} = \frac{\varepsilon''}{\varepsilon'} \tag{8}$$

giving a geometry independent measure for the dielectric loss. As can be seen from Figure 11 the capacitance of three devices that are namely "the same" (built the same way with the same

parameters) shows a slightly different absolute value, which is attributed to small thickness variations of the PVA film due to the spin coating process. As  $\tan \delta$  is the ratio of the real and the imaginary part of the capacitance (both of which depend on the geometry),  $\tan \delta$  is geometry independent, as can also be seen from Figure 11. From these measurements the dielectric permittivity of PVA has been calculated via equation (7):  $\varepsilon'_{PVA} = 6.1$  at 100 Hz.

**Figure 11:** Frequency dependent dielectric spectroscopy of a MIM (Al / PVA / Al) device.

The basic equation to describe dipolar relaxation processes in an harmonically alternating electric field  $\overline{E} = E_m e^{j\omega t}$  is the Debye relaxation equation [190]:

$$\varepsilon^*(\omega) = \varepsilon'(\omega) - i\varepsilon''(\omega) = \varepsilon_{\infty} + \frac{\varepsilon_s - \varepsilon_{\infty}}{1 + i\omega\tau}$$

(9)

where  $\varepsilon_s$  is the static permittivity ( $\omega \to 0$ ) and  $\varepsilon_{\infty}$  is the permittivity at high frequencies ( $\omega \to \infty$ ). This equation can be split into the real and the imaginary part [190]:

$$\varepsilon'(\omega) = \varepsilon_{\infty} + \frac{\varepsilon_{s} - \varepsilon_{\infty}}{1 + \omega^{2} \tau^{2}}$$

(10)

$$\varepsilon"(\omega) = \frac{\left(\varepsilon_s - \varepsilon_{\infty}\right)\omega\tau}{1 + \omega^2\tau^2} \tag{11}$$

$\varepsilon$ "( $\omega$ ) scales with  $\frac{\omega \tau}{1 + \omega^2 \tau^2}$ , which has a maximum for  $\omega \tau = 1$ . Therefore a single dipole gives a peak in  $\varepsilon$ "( $\omega$ ) and a dipole distribution may give a broader peak. An additional loss mechanism besides moving dipoles comes from electrical conductivity  $\sigma$ , which has to be added to  $\varepsilon^*(\omega)$  [190]:

$$\varepsilon^*(\omega) = \varepsilon_{\infty} + \frac{\varepsilon_s - \varepsilon_{\infty}}{1 + i\omega\tau} - \frac{i\sigma}{\omega}$$

(12)

As PVA has an amorphous and a polycristalline phase, it can be described as a two phase system with two phases with a certain volume fraction and different ionic conductivity. Such a system can be described as a matrix material with a complex permittivity  $\varepsilon_m^*(\omega)$  where "filler particles" (crystalline phase) are dispersed in the matrix with a complex, frequency-dependent permittivity  $\varepsilon_f^*(\omega)$  and volume fraction  $\varphi_f$ . According to the Maxwell-Wagner-Sillars (MWS) theory  $\varepsilon^*(\omega)$  of such a heterogenous mixture can be described by [192]:

$$\varepsilon^*(\omega) = \varepsilon_{\infty} + \frac{\Delta \varepsilon(n, \varphi_f, \sigma_m, \sigma_f)}{1 + i\omega\tau}$$

(13)

In this equation  $\Delta \varepsilon$  is a function of the shape factor, n, which describes the geometry of the filler particles. The conductivities  $\sigma_f$  and  $\sigma_m$  account for the conductivity of mobile charge carriers (e.g. electrons, holes, ions) in the matrix and in the filler region, respectively. A similar model has been suggested for microcrystalline Si TFTs, which consist of a heterogenous mixture of amorphous and crystalline Si [193].

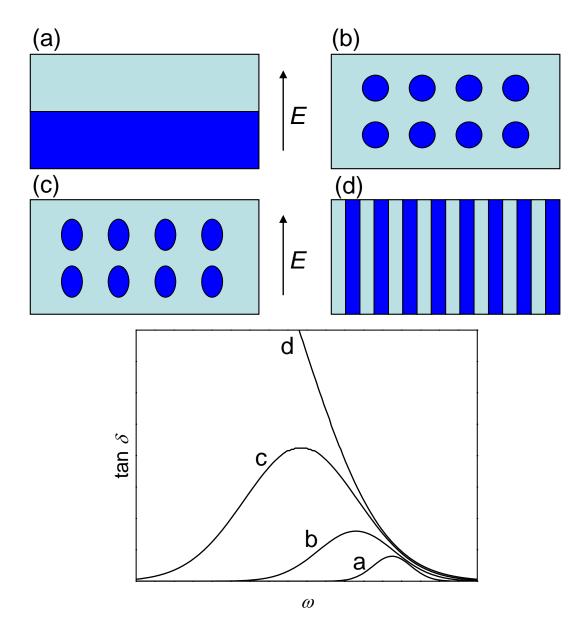

In addition mobile charges in a multicomponent dielectric with different conductivities result in a drastic increase of  $\varepsilon'$  by several orders of magnitude at low frequencies. In such systems the dielectric loss drastically depends on the shape factor of the filler particles, as schematically shown in Figure 12. Mixing the two materials to a heterogenous system causes an increased loss according to the MWS theory [194, 195, 196], where moving charges cause an additional interfacial polarization ( $P_i$ ) between matrix and filler material.  $P_i$  is low in case of a single interface (a) or flat lense like particles (not shown).  $P_i$  grows for spherical particles

(b) and increases further for upright ellipsoids (c). In case of interfaces parallel to the electric field E there is no interfacial polarization, but only Ohmic conduction resulting in an  $1/\omega$  behaviour (d) according to equation (12) and equation (7).

**Figure 12:** Influence of the shape of conducting filler particles on  $\tan \delta$  according to MWS polarization. E indicates the direction of the electric field.

An additional parameter that can influence dielectric spectroscopy results is temperature (T): The conductivity, in general, is temperature dependent, because the mobility of charge

carriers in the electric field is temperature dependent. If T approaches the glass transistion temperature  $T_g$ , also  $\varphi_f$ ,  $\sigma_m$ ,  $\sigma_f$  and n become T dependent:

$$\varepsilon^*(\omega) = \varepsilon_{\infty} + \frac{\Delta \varepsilon(n(T), \varphi_f(T), \sigma_m(T), \sigma_f(T))}{1 + i\omega\tau}$$

(14)

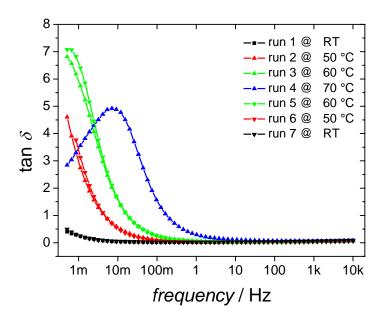

One more effect may occur for mobile ions in a dielectric when the dielectric is sandwiched between two metal electrodes: electrode polarization [196, 197, 198]. Electrode polarization is the phenomenon by which ions buildup at electrodes during low frequency measurements, assuming ion-blocking and non-injecting electrodes. Electrode polarization can be represented by a single Debye relaxation, similar to MWS polarization (compare equations (9) and (13)). For the case of fixed negative charges and mobile positive charges, the diffusion time relaxation  $\tau$  for electrode polarization is defined by

$$\tau = \frac{\varepsilon_{mat}}{\sigma_0} = \frac{\varepsilon_{mat}}{p_0 q \mu} \tag{15}$$

where  $\varepsilon_{\it mat}$  is the matrix dielectric constant,  $p_0$  is the equilibrium number density of free positive charges with mobility  $\mu$  and  $\sigma_0$  is the dc conductivity. Equation 15 shows that the ion concentration ( $p_0$ ) is proportional to the conductivity and inverse proportional to  $\tau$ . From this and equation 11 follows that an increased ion concentration causes a shift of the tan  $\delta$  peak to higher frequencies.

#### 1.3.2. MIS structures

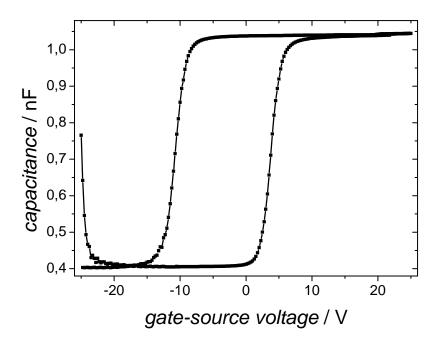

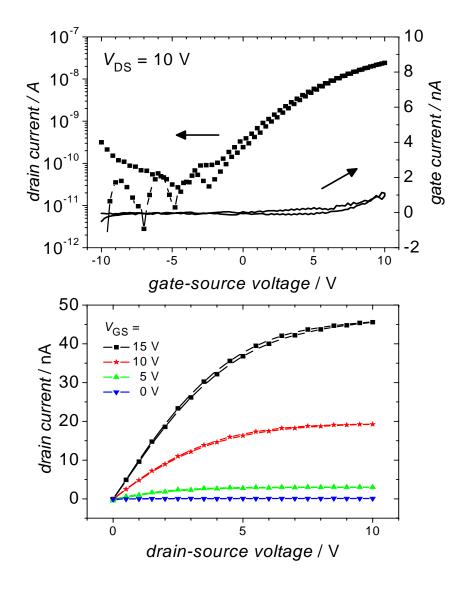

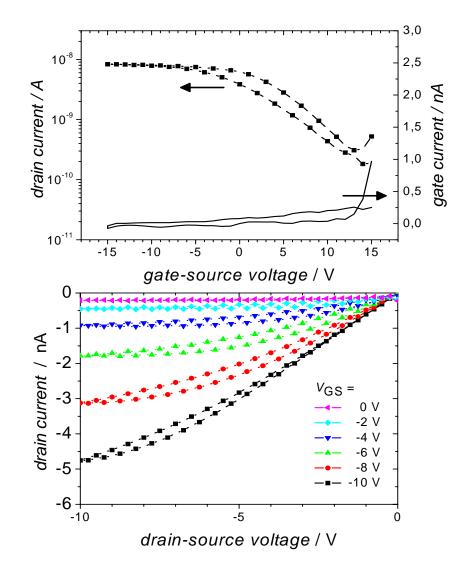

Dielectric spectroscopy is not limited to MIM structures. Also MIS structures, which are one step closer to the OFET geometry, can be investigated:

Voltage dependent dielectric spectroscopy of MIS structures can be used to distinguish between n-type and p-type semiconductors. When charges are injected into the semiconductor, the effective thickness of the capacitor decreases which causes an increase in the capacitance. Figure 13 shows an increase in the capacitance for positive "gate" voltages, because electrons can be injected from the other electrode into the  $C_{60}$  layer. These charges accumulate at the semiconductor / dielectric interface. Furthermore, if hysteresis is observed

in the transfer characteristics of an OFET, it *must* also be observed in the voltage dependent capacitance of a corresponding MIS structure, as shown in Figure 13.

**Figure 13:** Dielectric spectroscopy of a MIS device: Al / 500 nm PVA / 100 nm  $C_{60}$  / Al at 0.1 Hz showing an increase in capacitance at positive voltages due to the n-type semiconducting behaviour of  $C_{60}$ . Also present is hysteresis due to ions in the PVA.

# 2 EXPERIMENTAL

#### 2.1. Materials

## 2.1.1. Poly(vinyl alcohol)

Poly(vinyl alcohol) (PVA) is a white-yellowish non-toxic solid. Depending on the degree of polymerization the molecular weight ( $M_w$ ) is between 20000 and 200000 g/mol. Products with different degree of hydrolysis (depending on the degree of conversion during the transesterification, see below) are available. Standard products have 98-99 or 87-89 Mol-% of hydroxyl groups, with glass transition temperatures ( $T_g$ ) of 85°C and 58°C, and with melting points ( $T_m$ ) of 228°C and 186°C, respectively [199, 200]. PVA is hygroscopic and can take up to 25 % of water from humid ambient air [201, 202]. Furthermore, the tendency of PVA to crystallize is well documented [200].

Several grades of PVA were investigated. The "normal grade" was bought from Sigma Aldrich (Mowiol 40-88). Sigma Aldrich re-sells the normal grade produced by Kuraray. PVA is produced via poly(vinyl acetate), because vinylalcohol does not exist in large quantitites due to the keto-enol-tautomerism:

Vinylacetate is polymerized to poly(vinyl acetate):

$$n \longrightarrow * \bigcirc Ac$$

To convert the acetate into the alcohol the polymer has to be heated in methanol (MeOH) with NaOH. The methanolysis (a transesterification, reaction 1) leads to PVA and methylacetate (MeAc). After the methanolysis the basic solution has to be neutralized (reaction 2):

\*

$$+$$

MeOH  $\xrightarrow{\text{MeOH}}$   $\xrightarrow{\text{MeOH}}$   $\xrightarrow{\text{MeOH}}$   $\xrightarrow{\text{MeOH}}$   $\xrightarrow{\text{Na}^+ O^-}$   $+$  Na $^+ O^ +$  NeAc  $+$  H<sub>2</sub>O 2.) CH<sub>3</sub>COOH

The neutralization of NaOH with acetic acid (CH<sub>3</sub>COOH) results in sodium acetate (NaAc or CH<sub>3</sub>COO Na<sup>+</sup>). Both NaAc and PVA are water soluble, therefore it is not straightforward to separate them. The residual amount of NaAc in the "normal grade" PVA is specified to be < 0.5 mass% (usually around 0.3 mass%).

As it is known [200] that mobile ions in PVA cause problems in some electronic applications, an "electronic grade" PVA (Mowiol®40-88) with a reduced amount of NaAc is also available from *Kuraray Specialities Europe KSE GmbH*, *Germany*. The NaAc concentration in this "electronic grade" (also known as "low ash" grade) PVA is specified to be < 0.09 mass%.

The as received "electronic grade" PVA was further cleaned by dialysis giving the "dialysis grade" PVA: An aqueous PVA solution was filled into a dialysis tubing (high retention cellulose tubing, Sigma Aldrich, D0530). This membrane tubing is specified to retain >99% of Cytochrome C ( $M_w$  = 12400 g/mol) over a 10 hour period. As  $M_w$ (PVA) ~ 205000 g/mol it can be assumed that also >99 % of the PVA is retained. The filled and closed dialysis tubing is submerged in ultra pure water (,,18 M $\Omega$  water") which is stirred over night. Due to the concentration difference small ions and small molecules (also very short PVA chains) diffuse

from the PVA solution through the membrane into the water. As most of the PVA chains are too large to diffuse through the membrane, the PVA solution is purified. It is worth taking into account that osmosis can cause a dilution of the PVA solution.

The residual ion concentration in the PVA could be determined by quantifying the residual amount of ash after burning the whole PVA, but this method needs large amounts of material. Another useful method is atomic absorption spectroscopy (AAS), which can analyze dilute PVA solutions. The measurements confirmed the specifications for the "normal grade" (<0.5 mass% NaAc in the PVA) and the "electronic grade" (<0.09 mass% NaAc in the PVA) PVA. The "dialysis grade" was below the detection limit (~0.01 mass% NaAc in the PVA). With x-ray photoelectron spectroscopy (XPS) not even traces of sodium could be detected [203].

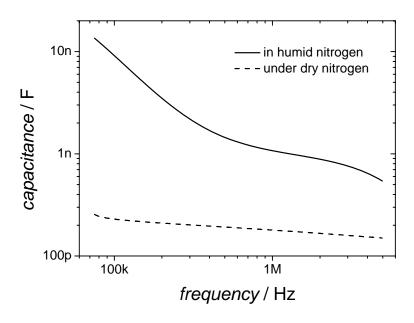

As stated above, PVA is hygroscopic and can take up to 25 % of water from humid ambient air [204, 205]. The high dielectric constant of water ( $\epsilon_{\rm H2O} \sim 80$  at RT [206]) causes a strong increase in the capacitance, as shown in Figure 14.

**Figure 14:** Dielectric spectroscopy of an Al / PVA / Al MIM device showing the increase in capacitance due to exposure to humidity.

### 2.1.2. Organic Semiconductors

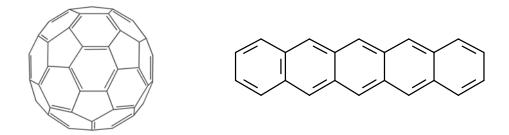

#### 2.1.2.1. Pentacene

Pentacene is an aromatic carbohydrate containing five linearly condensed benzene-rings, as shown in Figure 15, that is commonly used as p-type semiconductor. The darkblue crystalneedles melt at 271°C and decompose in air >300°C [199].

**Figure 15:** Schematic chemical structures of Buckminsterfullerene  $C_{60}$  (left) and pentacene (right).

#### 2.1.2.2. Buckminsterfullerene C<sub>60</sub>

Buckminsterfullerene ( $C_{60}$ ), first reported in 1985 [207], was used as n-type semiconductor.  $C_{60}$  (pureness 99.9 %) from *MER Corporation* (Arizona, USA) was used without further purification. The used  $C_{60}$  is a black crystalline powder with powder density of about 0.8 g/cc. Impurities are traces of  $C_{70}$  and  $C_{60}$  oxide [208]. Figure 15 shows the chemical structure of  $C_{60}$ .

# 2.2. Device Preparation

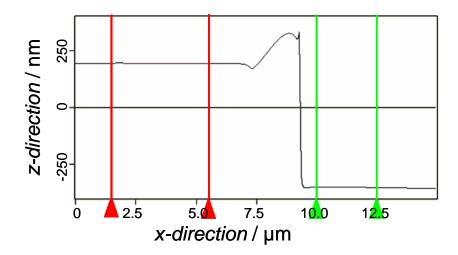

Glass substrates were cleaned in an ultrasonic bath using *Hellmanex*, DI water, acetone and isopropanole, respectively, each for 15 min. Depending on the desired device geometry (Figure 1 and Figure 16) the following layers were put onto the substrates:

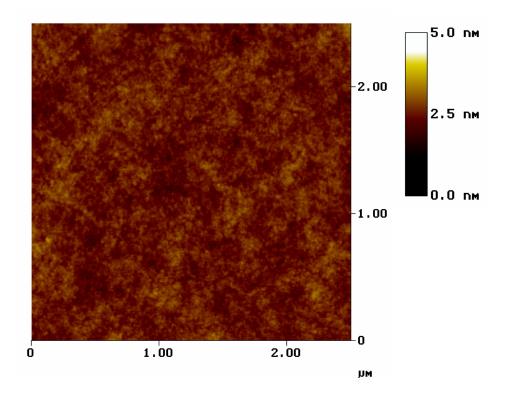

PVA film: For a 7 % solution, 70 mg of PVA were dissolved in 1 ml of hot ultra pure water. After cooling to RT the solution was filtered (*Whatman* 0,45  $\mu$ m) and spin coated (Spin Coater Model P6700: *Speciality Coating Systems, Inc.*, Indianapolis, USA) onto the substrate giving smooth (compare Figure 40) PVA films with a thickness of  $\sim 1 \mu$ m.

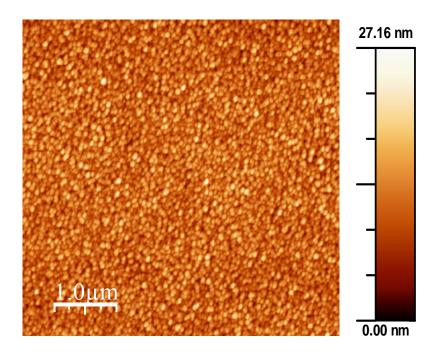

$C_{60}$  or pentacene were thermally evaporated in an Univex 350 (*Leybold Vacuum*, Cologne, Germany) high vacuum (p <  $5x10^{-6}$  mbar) system at a rate of 0.16 nm/s resulting in 100 nm thick films.

For the electrodes 100 nm thick aluminium films were thermally evaporated in an evaporation system (*Leybold Vacuum*, Cologne, Germany) inside a nitrogen glovebox (M. Braun, Garching, Germany). Shadow masks defined the electrode geometry: MIM structures had active areas of 2.5 mm<sup>2</sup>. For OFETs the channel length (L) and the channel width (W) were 100  $\mu$ m and 1 mm, respectively.

**Figure 16:** Different device geometries investigated in this work: (a) MIM, (b) MIS and (c) bottom gate staggered OFET structure. Source (S), drain (D), gate (G), electrode 1 (E1), electrode 2 (E2), semiconductor (SC) and dielectric (DE).

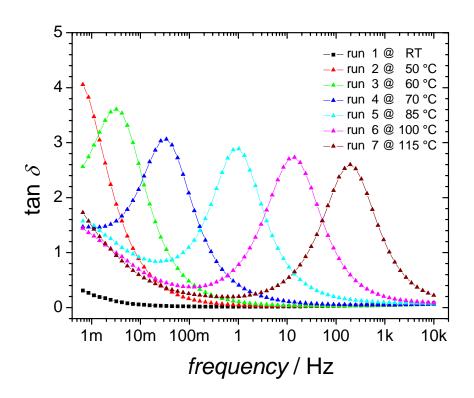

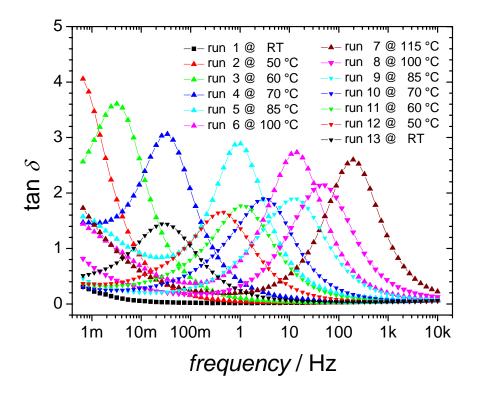

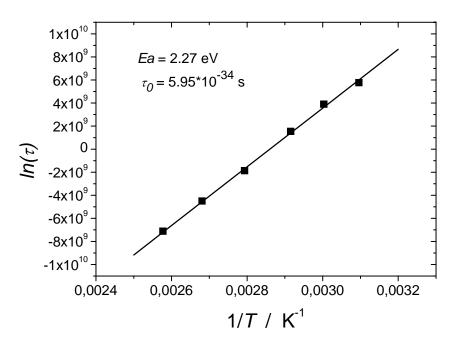

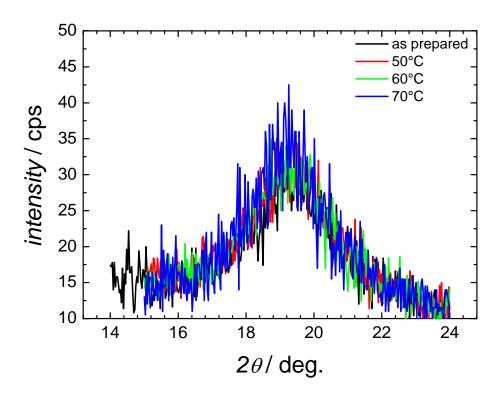

# 2.3. Current voltage measurements